Code: 13A04504

## B.Tech III Year I Semester (R13) Supplementary Examinations November/December 2017

## **DIGITAL IC APPLICATIONS**

(Electronics & Communication Engineering)

Time: 3 hours Max. Marks: 70

## PART - A

(Compulsory Question)

1 Answer the following:  $(10 \times 02 = 20 \text{ Marks})$

- What are the advantages and disadvantages of CMOS technology? (a)

- List out the characteristics of ECL. (b)

- What are the data types available in VHDL? (c)

- What is binding? (d)

- (e) Write a VHDL program for 2×4 decoder.

- Write a VHDL program for 1×4 demultiplexer. (f)

- (g) What is structural style of modeling?

- Convert a D flip-flop into T flip-flop. (h)

- Distinguish between SRAM and ROM. (i)

- (i) List out the applications of RAM.

## PART - B

(Answer all five units, 5 X 10 = 50 Marks)

UNIT – I

- 2 (a) With reference to the dynamic behavior of CMOS explain about speed and power dissipation of CMOS circuits.

- Design CMOS transistor circuit for 3-input AND gate. With the help of function tables explain the (b) operation of the circuit diagram.

OR

- 3 Draw the circuit diagram of basic TTL NAND gate and explain the three parts with the help of functional (a) operation.

- (b) Explain the following terms with reference to TTL circuit:

- (i) Logic levels. (ii) DC noise margin. (iii) High state fan-out.

[ UNIT – II ]

- Explain about dataflow design elements of VHDL. (a)

- Explain the difference in program structure of VHDL and any other procedural language. Give an (b) example.

OR

- Give the syntax and structure of a package in VHDL. 5 (a)

- Write a process based VHDL program for the prime-number detector of 4-bit input and explain the flow using logic circuit.

( III – III )

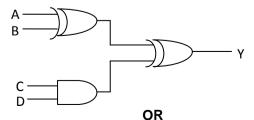

Obtain logical expression for the logic circuit shown and build the function with 8 to 1 (74x151) 6 multiplexer. Assume BCD are select lines of 74x151.

Design a 4x4 combinational multiplier and write the VHDL program in data flow model. 7

Contd. in page 2

R13

Code: 13A04504

UNIT - IV

- 8 (a) Draw the logic diagram of IC 74180 parity generator checker and explain its operation with the help of a truth table.

- (b) With neat, sketch explain Barrel shifter.

OR

- 9 (a) Explain how a JK-flip-flop can be constructed using a T-flip-flop.

- (b) Give a VHDL code for a 4-bit up counter with enable and clear inputs.

UNIT - V

- Write short notes on the following:

- (a) Two dimensional decoding.

- (b) Read / write operation of DRAM.

OR

Determine the ROM size needed to realize the logic function performed by 74x153 and 74x139.

\*\*\*\*